| Introduction | Scheduling | Example  | Utilization | AMC    | Results | Conclusions | Extra |

|--------------|------------|----------|-------------|--------|---------|-------------|-------|

|              |            |          |             |        |         |             |       |

|              |            |          |             |        |         |             |       |

|              |            |          |             |        |         |             |       |

|              |            |          |             |        |         |             |       |

|              |            |          |             |        |         |             | _     |

|              | Mixed-     | Critical | lity Sch    | edulir | ng with |             |       |

#### Eric Missimer, Katherine Missimer, Richard West

J

Boston University Computer Science

| Introduction | Scheduling |  | AMC | Conclusions |  |

|--------------|------------|--|-----|-------------|--|

| Introdi      | uction     |  |     |             |  |

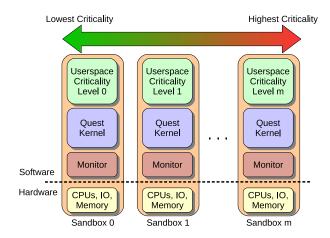

- Previously developed Quest-V separation kernel for mixed-criticality systems

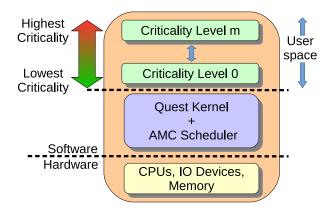

- Mixed-criticality now applied to single Quest kernel

- Mixed-criticality scheduling in presence of I/O

- Work builds on Quest's hierarchical VCPU scheduling framework

### Quest-V Mixed-Criticality Support

Quest-V – each sandbox has a single criticality level

Quest or a single Quest-V sandbox - multiple criticality levels

Introduction Scheduling Example Utilization AMC Results Conclusions Extra

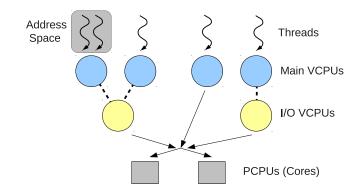

Quest Virtual CPUs (VCPUs)

Scheduling hierarchy: threads  $\rightarrow$  VCPUs  $\rightarrow$  PCPUs

|       | Scheduling | Example | AMC | Conclusions |  |

|-------|------------|---------|-----|-------------|--|

| Quest | VCPUs      |         |     |             |  |

- Two classes

- Main  $\rightarrow$  for conventional tasks

- $I/O \rightarrow$  for I/O event threads (e.g., ISRs)

- Scheduling policies

- Main  $\rightarrow$  Sporadic Server (SS)

- ▶  $I/O \rightarrow$  Priority Inheritance Bandwidth-preserving Server (PIBS)

|        | Scheduling | Example      | AMC | Conclusions |  |

|--------|------------|--------------|-----|-------------|--|

| SS Sch | eduling    | <del>,</del> |     |             |  |

- Each SS VCPU has pair (C,T)

- ► Guarantee budget (C) every period (T) when runnable

- Rate-monotonic scheduling theory applies

|        | Scheduling | Example | AMC | Conclusions |  |

|--------|------------|---------|-----|-------------|--|

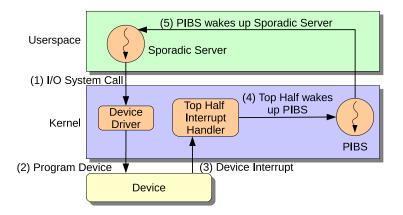

| PIBS S | Scheduli   | ng      |     |             |  |

- ► Each I/O VCPU has utilization factor U<sub>IO</sub>

- I/O VCPU inherits period & priority from Main VCPU that caused I/O request

- $\blacktriangleright T_{IO} = T_{Main}$

- $\bullet \ C_{IO} = U_{IO} \times T_{Main}$

- ▶ I/O VCPU eligible to execute at  $t_e = t + C_{actual}/U_{IO}$

- ▶ t =start of latest execution (>= previous eligibility time)

|        | Scheduling |       |    | AMC | Conclusions |  |

|--------|------------|-------|----|-----|-------------|--|

| Schedu | uling Fra  | amewo | rk |     |             |  |

Task & interrupt (CPU & I/O) scheduling in Quest

|  | Example | AMC | Conclusions |  |

|--|---------|-----|-------------|--|

|  |         |     |             |  |

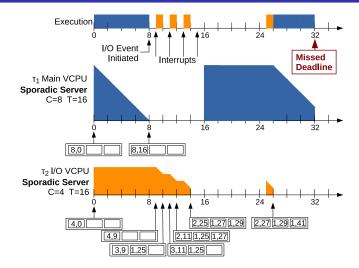

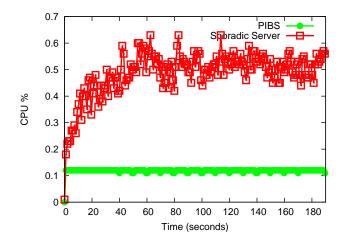

## Sporadic Server Only

Sporadic Server only example – replenishment list fills up, more scheduling events

| Scheduling | Example | AMC | Results | Conclusions |  |

|------------|---------|-----|---------|-------------|--|

|            |         |     |         |             |  |

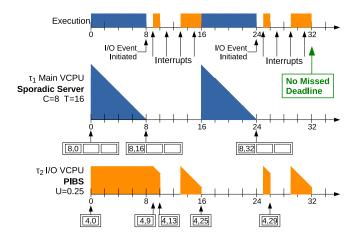

### Sporadic Server + PIBS

Sporadic Server + PIBS - no delayed replenishment due to fragmentation, less scheduling events

System of *n* Main and m I/O VPUs, and one PCPU

•

$$\sum_{i=0}^{n-1} \frac{C_i}{T_i} + \sum_{j=0}^{m-1} (2 - U_j) \cdot U_j \le n \cdot (\sqrt[n]{2} - 1)$$

- C<sub>i</sub> & T<sub>i</sub> are the budget capacity and period of Main VCPU V<sub>i</sub>

- $U_j$  is the utilization factor of I/O VCPU  $V_j$

IntroductionSchedulingExampleUtilizationAMCResultsConclusionsExtraPIBS Max Utilization in Main VCPU Period, T

U – Utilization of I/O VCPU running PIBS T – Period of Main VCPU

- AMC tasks defined by:

- Period  $(T_i)$ , Deadline  $(D_i)$

- Vector of Capacities  $(\overrightarrow{C_i})$  for each criticality level

- System operates in one of a set of criticality levels

- e.g., Criticality Level  $L \in \{LO, HI\}$

- HI-criticality task,  $C_i(HI) \ge C_i(LO)$

- LO-criticality task,  $C_i(HI)$  is undefined

- System starts in L0-criticality mode

- If a task uses its entire capacity and does not signal job completion, the system switches into HI-criticality mode

- Only HI-criticality tasks run in HI-criticality mode, using their C<sub>i</sub>(HI) capacity

- Allows extra capacity to finish HI-criticality jobs before their deadlines

- Extended AMC to include PIBS for I/O requests

- Response time (schedulability) analysis considers

- when tasks are in HI-criticality mode

- when tasks are in LO-criticality mode

- when tasks switch from LO- to HI-criticality mode

- added interference by PIBS

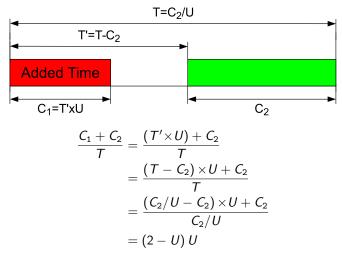

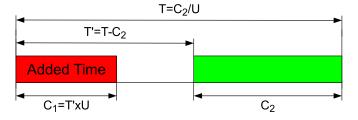

$C_1 = (T - C_2) \cdot U = (T - UT) \cdot U$

▶ We saw added execution time by a PIBS task is

Ι

$$C_1 = (T - C_2) \cdot U = (T - UT) \cdot U$$

• Added interference  $I_k^q$  by PIBS  $\tau_k$  assigned to SS  $\tau_q$ ...

$$egin{aligned} & {}_{k}^{q}\left(t

ight) = \left(T_{q}\!-\!T_{q}U_{k}

ight)U_{k} + \left\lceilrac{t}{T_{q}}

ight

ceil T_{q}U_{k} \ &= \left(1-U_{k}

ight)T_{q}U_{k} + \left\lceilrac{t}{T_{q}}

ight

ceil T_{q}U_{k} \ &= \left(1+\left\lceilrac{t}{T_{q}}

ight

ceil - U_{k}

ight)T_{q}U_{k} \end{aligned}$$

IO-AMC response time bound adds I<sup>q</sup><sub>k</sub> for each PIBS τ<sub>k</sub> to system of Sporadic Servers

- For each PIBS  $\tau_k$ , have a vector of utilizations  $\overline{U_k(L)}$  for each criticality level L

- If  $\tau_k$  is a HI-crit PIBS then  $U_k(\text{HI}) \ge U_k(\text{LO})$

- If  $\tau_k$  is a LO-crit PIBS then  $U_k(LO) > U_k(HI)$

- Then I<sup>q</sup><sub>k</sub>(t, L) is the interference by PIBS τ<sub>k</sub> assigned to SS τ<sub>q</sub> at time t in criticality level L

|       |         |       | AMC | Results | Conclusions |  |

|-------|---------|-------|-----|---------|-------------|--|

| Quest | Experin | nents |     |         |             |  |

| Task $C$ (L0) or $U$ (L0)     |                           | C (HI) or $U$ (HI) | T             |

|-------------------------------|---------------------------|--------------------|---------------|

| Camera Task                   |                           |                    |               |

| (HI-criticality) 23 <i>ms</i> |                           | 40 <i>ms</i>       | 100 <i>ms</i> |

| CPU Task                      |                           |                    |               |

| (LO-criticality)              | 10 <i>ms</i>              | 1 <i>ms</i>        | 100 <i>ms</i> |

| Bottom Half                   |                           |                    |               |

| (PIBS)                        | $U\left(	t{LO} ight)=1\%$ | $U({	t HI})=2\%$   | 100 <i>ms</i> |

| Bottom Half                   |                           |                    |               |

| (SS)                          | 1 <i>ms</i>               | 2 <i>ms</i>        | 100 <i>ms</i> |

Task Set Parameters - Bottom Half handles Camera interrupts

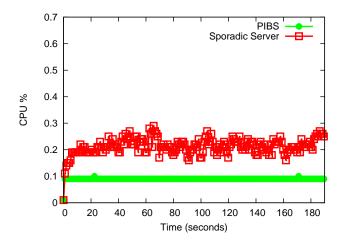

Quest on Intel Core i3-2100 @ 3.1KHz Camera – U(LO) = 1% (1ms/100ms), U(HI) = 2% (2ms/100ms) Scheduling overhead of SS-only scheme > SS+PIBS

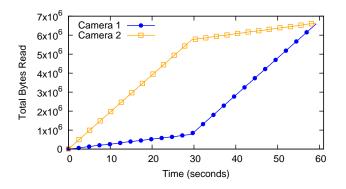

Camera 1 – U(LO) = 1% (1ms/100ms), U(HI) = 2% (2ms/100ms) Camera 2 – U(LO) = 2% (2ms/100ms), U(HI) = 1% (1ms/100ms)

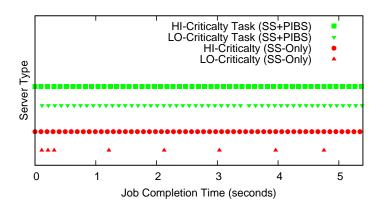

SS-only server for camera interrupts causes task on Main VCPU to deplete budget before job completion. Mode change with SS-Only causes L0-crit jobs to finish later. Introduction Scheduling Example Utilization AMC **Results** Conclusions Extra

# **Different Criticality Devices**

- Can assign criticality levels to devices to control bandwidth

- Mode change at 30 seconds

- Camera 1 U(LO) = 0.1%, U(HI) = 1%

- Camera 2 U(LO) = 1%, U(HI) = 0.1%

- Added IO-AMC support to Quest RTOS

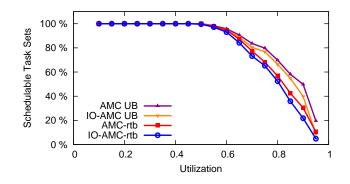

- Simulations (& analysis) show SS for both tasks & interrupt handlers is theoretically better than SS+PIBS

- Expts show PIBS for interrupt handling incurs lower practical costs

- Ability to assign criticality levels to devices

- Future work to consider more complex scenarios where blocking I/O delays impact task execution

| Scheduling |  | AMC | Results | Conclusions | Extra |

|------------|--|-----|---------|-------------|-------|

|            |  |     |         |             |       |

#### Scheduling Results

500 random task sets per utilization [see paper]. Theoretical performance of IO-AMC-rtb slightly worse than AMC-rtb. This is due to the extra interference PIBS can cause compared to an equivalent Sporadic Server.