# **Time-constrained Reactive Automata**

### A NOVEL DEVELOPMENT METHODOLOGY FOR

### Embedded Real-time Systems

A thesis presented

$_{

m by}$   ${\cal A}_{

m zer} \, {\cal B}_{

m estavros}$

$\mathrm{to}$

### The Division of Applied Sciences

in partial fulfillment of the requirements

for the degree of

### Doctor of Philosophy

in the subject of

### **Computer Science**

### HARVARD UNIVERSITY

Cambridge, Massachusetts

August 1991

©1991 by Azer Bestavros All rights reserved "Hear, my child, the instruction of thy father, and forsake not the teaching of thy mother; For they are a fair garland upon thy head, and adorning pendants for thy neck."

Proverbs 1:8-9

To  $\mathcal{M}$ om and  $\mathcal{D}$ ad.

# **Time-constrained Reactive Automata**

### A NOVEL DEVELOPMENT METHODOLOGY FOR

### Embedded Real-time Systems

# Abstract

Embedded computing systems are characterized by the rigidity of their performance and reliability requirements, which are dictated by the critical nature of their missions and the demanding and often hostile environments with which they interact. Considering the vital role that such systems are playing and will continue to play in our world, it has become imperative that a rigorous and systematic treatment that recognizes their unique requirements be adopted. In this thesis we propose such a treatment based on the Time-constrained Reactive Automata (TRA) model – a novel formalism suitable for the specification, validation, verification, and implementation of embedded systems.

Previous studies in modeling real-time computing have focussed on adding the notion of time to formal modeling techniques of traditional systems without regard to physical realities of the modeled systems. The TRA model is a physically sound formalism. Among its salient features is a fundamental notion of space and time that restricts the expressiveness of the model in a way that allows the specification of only those systems that are potentially physically realizable. The TRA model is compositional and supports time, control, and computation non-determinism without violating the principles of causality and spontaneity.

Using the TRA model, an embedded system is viewed as a set of asynchronously interacting automata (TRAs), each representing an autonomous system entity. TRAs are input enabled; they interact by signaling events on their output channels and by reacting to events signaled on their input channels. The behavior of a TRA is governed by time-constrained causal relationships between computation-triggering events. The TRA model is compositional and allows time, control, and computation non-determinism. The TRA model allows the representation of both the external environment and the programmed system along with the available computational resources in a unique framework making it possible to prove safety and liveness properties and study transient and steady state performances of embedded real-time control systems. In particular, using the TRA formalism there is no conceptual distinction between a system and a property; both are specified as formal objects. This reduces the verification process to that of establishing correspondences – preservation and implementation – between such objects.

CLEOPATRA is a specification language based entirely on the TRA formalism. It features a C-like imperative syntax for the description of computation, which makes it easier to incorporate in real applications already using C; it is object-based, thus advocating modularity, reusability, and off-the-shelf hierarchical programming of embedded systems. CLEOPATRA is semantically sound. In particular, its objects can be transformed, mechanically and unambiguously, into formal TRA objects for verification purposes. We have developed a compiler that allows specifications written in CLEOPATRA to be executed in simulated time, thus providing a valuable tool for validation purposes.

We have used the TRA development methodology in the design, simulation, and analysis of various systems – specifically asynchronous digital circuits, sensori-motor activity management for autonomous systems, and intelligent controllers. Our experience has confirmed the suitability of this novel methodology for the specification, verification, and validation of embedded and time-critical applications. Its usefulness in the implementation of such systems, although not tackled in this thesis, is eminent.

# Contents

|   | Abs             | stract  |                                      | v   |

|---|-----------------|---------|--------------------------------------|-----|

|   | List of Figures |         |                                      | x   |

|   | Ack             | nowlee  | dgments                              | xii |

| 1 | Intr            | roducti | lon                                  | 1   |

|   | 1.1             | Embeo   | dded Systems                         | 2   |

|   |                 | 1.1.1   | Aspects and Constraints              | 2   |

|   |                 | 1.1.2   | Development Requirements             | 4   |

|   | 1.2             | Thesis  | Outline                              | 5   |

| 2 | A S             | urvey   | of Related Research                  | 6   |

|   | 2.1             | Forma   | l Models and Verification Techniques | 7   |

|   |                 | 2.1.1   | State-based Techniques               | 8   |

|   |                 | 2.1.2   | Process-Algebra-based Techniques     | 9   |

|   |                 | 2.1.3   | Logic-based Techniques               | 10  |

|   |                 | 2.1.4   | Petri-net-based Techniques           | 11  |

|   | 2.2             | Specifi | ication Techniques                   | 12  |

|   |                 | 2.2.1   | Requirement Specification Languages  | 12  |

|   |                 | 2.2.2   | Programming Languages                | 14  |

|   | 2.3             | Develo  | opment Support                       | 17  |

|   |                 | 2.3.1   | Operating System Kernels             | 18  |

|   |                 | 2.3.2   | Scheduling Algorithms                | 19  |

|   | 2.4             | Other   | Issues                               | 20  |

| 3 | The  | Time    | -constrained Reactive Automata Model          | <b>21</b> |

|---|------|---------|-----------------------------------------------|-----------|

|   | 3.1  | Novelt  | iies                                          | 22        |

|   | 3.2  | The $T$ | RA Model                                      | 23        |

|   |      | 3.2.1   | Basic Definitions                             | 24        |

|   |      | 3.2.2   | The TRA Object                                | 27        |

|   |      | 3.2.3   | Sources of Non-determinism                    | 31        |

|   | 3.3  | Space   | and Time aspects of TRAs                      | 32        |

|   |      | 3.3.1   | The Conflict Relationship                     | 32        |

|   |      | 3.3.2   | Proper TRAs                                   | 33        |

|   |      | 3.3.3   | TRA Control Components                        | 33        |

|   | 3.4  | The T   | RA Operational Semantics                      | 36        |

|   |      | 3.4.1   | TRA Intentions, Status, and Status Succession | 36        |

|   |      | 3.4.2   | TRA Executions, Schedules, and Behaviors      | 39        |

|   |      | 3.4.3   | TRA Implementation                            | 41        |

|   |      | 3.4.4   | TRA Equivalence                               | 42        |

|   |      | Opera   | tions on TRAs                                 | 43        |

|   |      | 3.5.1   | Hiding                                        | 43        |

|   |      | 3.5.2   | Renaming                                      | 44        |

|   |      | 3.5.3   | Composition                                   | 45        |

| 4 | TRA- | based   | Specification                                 | 50        |

|   | 4.1  | CLEO    | PATRA: A Specification Language               | 51        |

|   |      | 4.1.1   | Classes and Objects                           | 51        |

|   |      | 4.1.2   | Time-constrained Event-driven Transaction     | 55        |

|   |      | 4.1.3   | An Example                                    | 58        |

|   | 4.2  | Relatio | onship between $CLEOPATRA$ and the TRA model  | 60        |

|   |      | 4.2.1   | Soundness                                     | 60        |

|   |      | 4.2.2   | Completeness                                  | 64        |

| 5 | TRA- | based   | Verification                                  | 66        |

|   | 5.1  | Modul   | lar Decomposition                             | 67        |

|   | 5.2  | Functi  | ional Decomposition                           | 72        |

|   | 5.3  |         | chical Decomposition                          | 73        |

| 6 | TRA | -based                 | Validation                                                                                                               | <b>79</b> |

|---|-----|------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 6.1 | CLEO                   | PATRA: A Simulation Language                                                                                             | 80        |

|   |     | 6.1.1                  | Data Types                                                                                                               | 80        |

|   |     | 6.1.2                  | The main TRA-class                                                                                                       | 81        |

|   |     | 6.1.3                  | Object Instantiation                                                                                                     | 81        |

|   |     | 6.1.4                  | ${\rm System-defined} \ TRA-classes \ \ \ldots $ | 83        |

|   |     | 6.1.5                  | $Compatibility with \ C  . \ . \ . \ . \ . \ . \ . \ . \ . \ .$                                                          | 85        |

|   |     | 6.1.6                  | Compilation and Execution                                                                                                | 85        |

|   | 6.2 | Simula                 | ation of Reactive Behaviors in $\mathcal{CLEOPATRA}$                                                                     | 88        |

|   |     | 6.2.1                  | Servo Control Systems (Basic Behaviors)                                                                                  | 88        |

|   |     | 6.2.2                  | Selective Control Systems (Subsuming Behaviors)                                                                          | 90        |

|   |     | 6.2.3                  | Teleo-selective Control Systems (Competing Behaviors) $\ldots \ldots$                                                    | 92        |

|   |     | 6.2.4                  | Intelligent Control Systems (Intelligent Behaviors)                                                                      | 93        |

| 7 | TRA | -based                 | Implementation                                                                                                           | 97        |

|   | 7.1 | CLEO                   | PATRA: A Programming Language                                                                                            | 98        |

|   | 7.2 | TRA-b                  | ased Development of Robotics Applications                                                                                | 99        |

| 8 | Cor | nclusio                | n                                                                                                                        | 103       |

|   | 8.1 | Summ                   | nary                                                                                                                     | 104       |

|   | 8.2 | Direct                 | tions for Future Research                                                                                                | 105       |

|   | Bib | liograp                | ohy                                                                                                                      | 107       |

|   | Ind | $\mathbf{e}\mathbf{x}$ |                                                                                                                          | 115       |

# List of Figures

| 3.1 | TRA objects and channels                                                   |

|-----|----------------------------------------------------------------------------|

| 3.2 | Signals, events, and actions                                               |

| 3.3 | Basic components of a TRA object                                           |

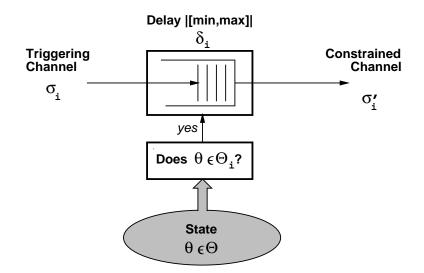

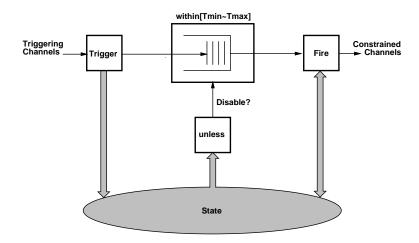

| 3.4 | A TRA time-constrained causal relationship                                 |

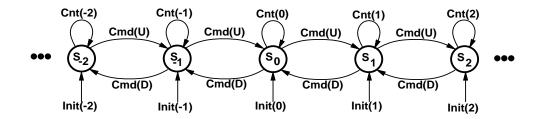

| 3.5 | State diagram of up/down counter                                           |

| 3.6 | TRA-specification of up/down counter                                       |

| 3.7 | An improper TRA specification of a counter                                 |

| 3.8 | A proper TRA specification of a counter                                    |

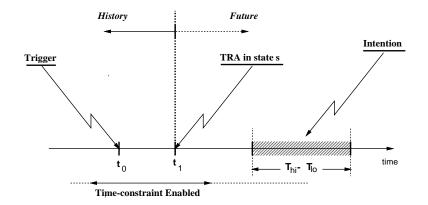

| 3.9 | The notion of a TRA status                                                 |

| 4.1 | Partial Syntax of a TRA specification in CLEOPATRA                         |

| 4.2 | Specification of the class of integrators that use the trapezoidal rule 53 |

| 4.3 | CLEOPATRA specification of a ramp generator                                |

| 4.4 | Time-constrained Event-driven Transaction (TET)                            |

| 4.5 | CLEOPATRA specification of the factorial computation                       |

| 4.6 | CLEOPATRA specification of a finite length FIFO delay element              |

| 4.7 | CLEOPATRA specification of a 2-input synchronizer                          |

| 4.8 | Formal TRA specification of a 2-input synchronizer                         |

| 5.1 | CLEOPATRA specification of the installations $X$ and $Y$                   |

| 5.2 | CLEOPATRA specification of the property $P$                                |

| 5.3 | TRA-specification of the property $\mathcal{P}$                            |

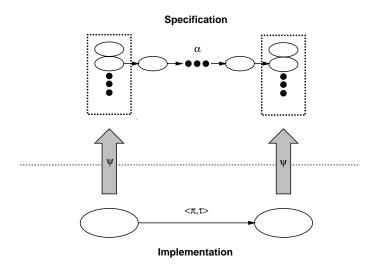

| 5.4 | $\Psi$ -mapping between specification and implementation                   |

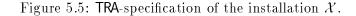

| 5.5 | TRA-specification of the installation $\mathcal{X}$                        |

| 5.6 | TRA-specification of the composition $\mathcal{X} \times \mathcal{C}$      |

| 6.1  | The main TRA-class                                                                                                                    | 82  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2  | A stand-alone process control system.                                                                                                 | 83  |

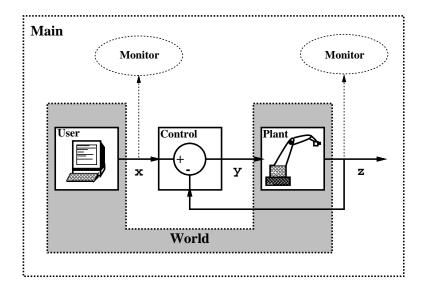

| 6.3  | Simulated behavior of an underdamped process control system                                                                           | 84  |

| 6.4  | The fmonitor system-defined TRA-class                                                                                                 | 84  |

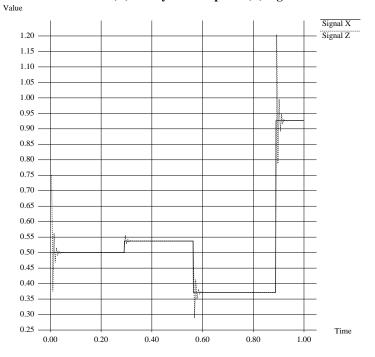

| 6.5  | Compilation and simulation of ${\cal CLEOPATRA}$ specifications                                                                       | 86  |

| 6.6  | A typical $\mathcal{CLEOPATRA}$ compilation and execution session                                                                     | 87  |

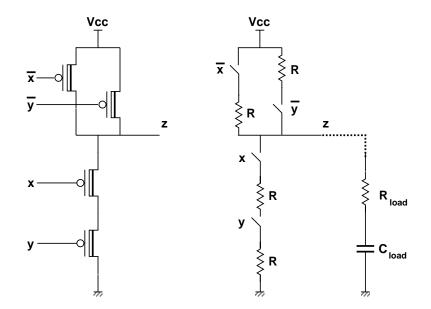

| 6.7  | $\mathrm{CMOS}\ \mathtt{nand}\ \mathrm{gate}\ \mathrm{and}\ \mathrm{a}\ \mathrm{switching}\ \mathrm{circuit}\ \mathrm{approximation}$ | 89  |

| 6.8  | ${\cal CLEOPATRA}$ specification of the nand gate                                                                                     | 89  |

| 6.9  | ${\cal CLEOPATRA}$ specification of the subsumption TRA                                                                               | 91  |

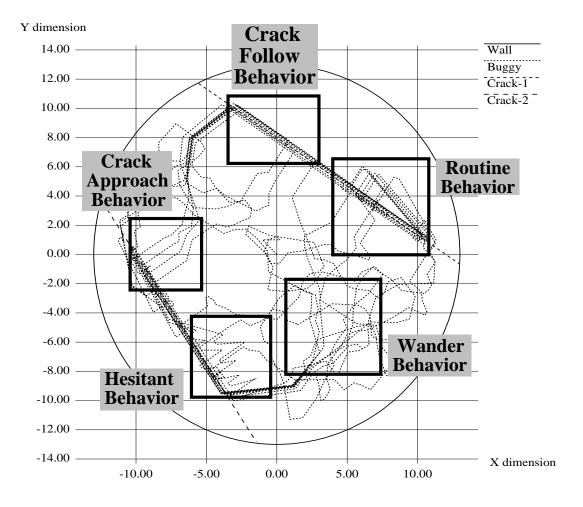

| 6.10 | Basic and emergent behaviors of Buggy in a typical simulation                                                                         | 94  |

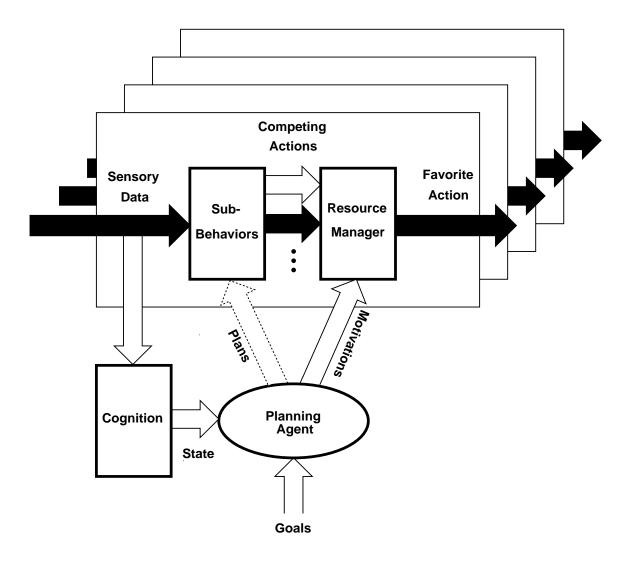

| 6.11 | Interaction between behavioral planning and real-time control                                                                         | 95  |

|      |                                                                                                                                       |     |

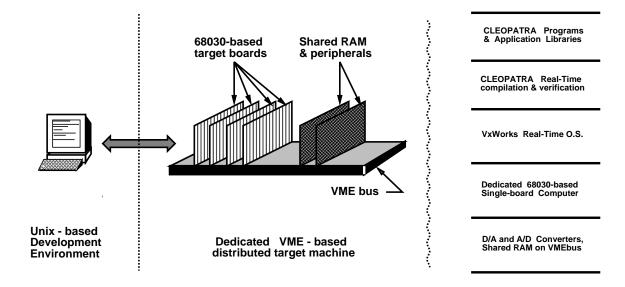

| 7.1  | Components of a $\mathcal{CLEOPATRA}$ -based implementation environment $\ldots \ldots$                                               | 99  |

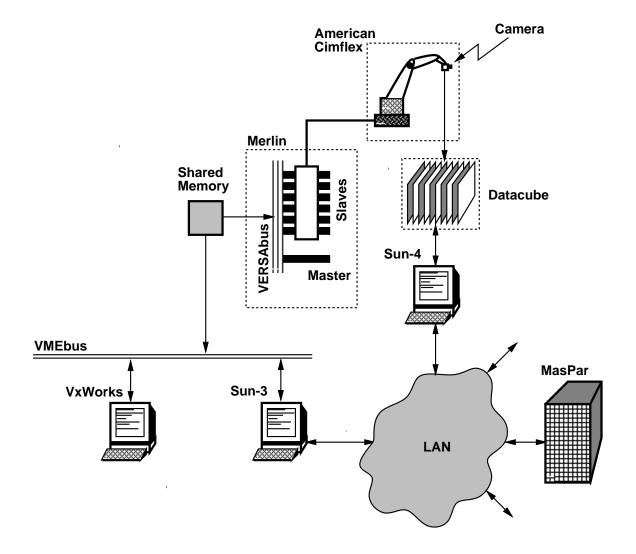

| 7.2  | Set-up for a sensori-motor activity coordination experiment                                                                           | 102 |

## Acknowledgments

$\mathcal{M}$ y first exposure to the difficulties involved in the development of embedded systems came in the summer of 1988 while working in the Robotics Laboratory of Harvard University on the implementation of an interface that allows the programmable control of an industrial robot arm from the Unix<sup>TM</sup>-based environment of a Sun<sup>TM</sup> workstation. The interface worked and my summer project was over, but my quest for a scientific methodology for the development of embedded computing systems was just starting. Almost three summers later, I am hereby presenting my findings.

This work would have been impossible if it were not for the advice, attention, and encouragement of many people; I wish to thank them all. I also owe much to Harvard University for the intellectual wealth and the cultural diversity of its community. I feel privileged to belong to this unique institution.

In the first place, I am greatly indebted to my advisor Professor Thomas E. Cheatham, Jr. for his constant encouragement and continued support during the course of this work. I am grateful to him for he has taught me, among many other things, the art of being a researcher. I am really fortunate for having been under his tutelage. Also, I would like to express my gratitude to the other members of my thesis committee, Professor Ugo Gagliardi and Professor James Clark, who helped me in my research from start to finish with valuable counseling and helpful suggestions.

I am most thankful to the faculty, students, and staff of the Computer Science Department at Harvard University for giving me the opportunity to work in such a stimulating, and yet personal, environment. In particular, I want to thank Dan Stefanescu, Michael Kilian, and all members of the Languages and Systems group for their feedback and discussion of the many lengthy presentations of my work. My thanks are also due to members of Harvard's Robotics Laboratory, especially to Nicola Ferrier, George Thomas, and John Page, for their technical assistance and for putting up with my growling experiments. A number of people have generously helped me in preparing and presenting my work; I am grateful to all of them. I am particularly appreciative of the constructive comments of Yves Deville and César Galindo-Legaria on the final manuscripts of this thesis.

Finally, I wish to acknowledge the tuition and guidance of Professors Michael Rabin, Roger Brockett, Nancy Lynch, Harry Lewis, Meichun Hsu, and many other scholars at Harvard University, Massachusetts Institute of Technology, and Alexandria University.

This work was supported by DARPA N00039-88-C-0163

# Chapter 1

# Introduction

$\mathcal{T}$  he use of computer systems to monitor and control realtime processes in industrial, medical, scientific, environmental, military, and other applications that are vital to our lives, continues to mushroom. The critical nature of these processes coupled with their inherent complexities, demand that a rigorous and systematic methodology be employed in their specification and implementation so as to guarantee a predictably safe operation. This thesis proposes such a treatment.

### 1.1 Embedded Systems

A computing system is *embedded* if it is explicitly viewed as being a component of a larger system whose primary purpose is to monitor and control an environment. The leaping advances in computing technologies that the last few decades have witnessed has resulted in an explosion in the extent and variety of such systems. This trend is likely to continue in the future.

### 1.1.1 Aspects and Constraints

Embedded systems are usually associated with critical applications, in which human lives or expensive machinery are at stake. Their missions are often long-lived and non-interruptible, making maintenance or reconfiguration difficult. Examples include command and control systems, nuclear reactors, industrial process-control plants, robotics, space shuttle and aircraft avionics, collision avoidance systems, automotive control, switching circuits and telephony systems, data-acquisition systems, and real-time databases, just to name a few.

Viewed simply, an embedded system has two parts: an *external interface* and a *programmed system*. The external interface consists of a number of devices such as sensors and actuators that interact with the environment. The programmed system collects information from the sensors and responds by producing actions to drive the actuators. The sustained demands of the environments in which such systems operate pose relatively rigid and urgent requirements on their performance. These requirements are usually stated as constraints on the real-time behavior of the programmed system. Wirth [Wirt77] singled out this processing-time dependency as the one aspect that differentiates embedded systems from other sequential and parallel systems. This led to a body of research on *real-time computing*, which, in many instances, was considered in isolation from other equally if not more important aspects of embedded systems. In particular, the critical nature of the missions associated with embedded systems fail to meet their specified reliability or performance requirements, they should do so safely [Leve91]. In addition to the aforementioned performance and reliability requirements, the development of embedded systems is often governed by a number of other constraints. In particular, tasks in an embedded application often compete for limited resources, like processors and actuators, thus giving rise to *resource constraints*. They might have to concurrently execute in order to achieve a desirable effect, thus imposing *concurrency constraints*. They might be suspended, or aborted in favor of a higher priority task, thus abiding by *precedence constraints*. They might have to communicate and synchronize to insure the satisfaction of *consistency constraints*. They might have to execute on specific sites or use specific resources to achieve *fault-tolerance constraints*. Finally, and perhaps most importantly, it is often the case that the application itself might dictate *logistic constraints* pertaining to physical aspects such as placement and packaging, or mechanical and inertial properties such as stability, steady state errors, and communication delays.

The range of disciplines employed in developing the various components of an embedded application makes it extremely difficult to adopt an accurate and integrated view of the system in its entirety. This further complicates the process of specifying and verifying system-wide requirements. For example, in a simple sensori-motor robotic application [Clar91], algorithms from various disciplines like low-level imaging, active vision, tactile sensing, path planning, compliant motion control, and non-linear dynamics may be utilized [Fu87]. Not only are these disciplines very different with respect to their abstractions and programming styles, but they also differ greatly in their computational requirements, which range from single-board dedicated processors to massively parallel general-purpose computers.

Current embedded systems are expensive to build and their properties are usually verified with ad hoc techniques, or with expensive and extensive simulations [Stan88a]. Minor specification or implementation changes result in new rounds of testing and fixing. The often incomplete and evolving specifications of these systems further exasperates this problem. Schneider [Schn88] portrays the situation aptly by saying that "Unlike other engineering disciplines, our methods are not founded on science. Real-time systems are built one way or another because that was the way the 'last one' was built. And, since the 'last one' worked, we hope that the next one will". This brute force approach is not likely to scale-up with future systems. A rigorous and systematic treatment of embedded systems that recognizes their unique requirements is imperative if we are to meet the needs and challenges of the future.

#### 1.1.2 Development Requirements

Predictability – the ability to foretell that an implementation will not violate a set of specification requirements – is a crucial, highly desirable property of embedded time-critical systems. Therefore, the success of any embedded system development methodology is largely judged based on the degree with which such a methodology enhances and promotes the predictability of the developed system.

Validation is the process of determining whether customers' desires have been correctly specified. The complexity of embedded systems renders the specification of their desired functionalities and constraints very difficult. A complete and correct set of requirements is seldom known a priori. *Prototyping* an implementation is often the approach used for validation purposes. Such an approach, although useful for simpler and massively produced systems, becomes impractical for complex, one-of-a-kind systems. *Simulations* are likely to be used instead. When a potential implementation is prototyped or simulated, both the specification and the realization are tested, which makes the isolation of customer and implementor responsibilities difficult and sometimes impossible. To solve this problem, the validation process has to be completely independent from implementation decisions. This is only possible if the system specifications are executable, and therefore can be used directly to generate demonstrable behaviors. *Executable specifications* have the added advantage that they help debug the customer's requirements early in the development cycle, before any investment in implementation takes place.

*Verification* is the process of certifying that certain desired properties<sup>1</sup> are preserved in a given set of system specifications. *Formal verification* entails proving analytically that the desired properties follow from the given specifications. This requires that both the specifications and the properties to be certified be formally expressed. Due to the grandeur

<sup>&</sup>lt;sup>1</sup>Safety (nothing bad will happen) or liveness (something good will happen) are examples of such properties.

and complexity of embedded systems, accurate mathematical representation is not always feasible. *Empirical verification*, relying on extensive testing of simulations and prototypes, has to be used instead.

As we hinted before, current approaches to the specification of an embedded system are notorious for their inaccuracy and incompleteness. This leads to frequent changes in the specification late in the development cycle. To be able to accommodate such changes gracefully, *modular* development methodologies, which support both functional and hierarchical decomposition, should be adopted to promote *reusability* and *adaptability*.

### **1.2** Thesis Outline

In chapter 2, we identify the various areas of research in embedded and real-time systems that have been addressed in the past few years and that need to be addressed in the future. In this respect, we single out the major research efforts in modeling and verification formalisms, specification and programming languages, and system development support.

In chapter 3, we present the backbone of our development methodology, namely the Time-constrained Reactive Automata (TRA) formalism. Following a brief overview of the guiding principles that motivated our choices, we formally present the basic components of the TRA model and its operational semantics. The remainder of the thesis is devoted to the various aspects of the TRA-based development of embedded real-time systems, namely specification, verification, validation, and implementation.

In chapter 4, we introduce CLEOPATRA, a TRA-based specification language. We establish the soundness of CLEOPATRA and characterize its expressiveness in relation with the TRA formalism. In chapter 5, we present three formal verification techniques for the TRA model based on modular, functional, and hierarchical decomposition of systems. In chapter 6, we introduce those ingredients of CLEOPATRA that allow it to be executable and, thus, suitable for validation purposes via simulation. In chapter 7, we discuss the potentials of CLEOPATRA to serve as a programming language for implementation purposes. We conclude in chapter 8 with a summary of contributions and future research directions.

## Chapter 2

# A Survey of Related Research

$\mathcal{I}n$  the past few years, various aspects of embedded and realtime systems have been studied, namely formal models, specification techniques, verification methodologies, development tools, and operating systems. The absence of a unifying formal framework that addresses the aforementioned issues severely limits the usefulness of these studies. Wirth classified computation into three categories: sequential, parallel, and processing-time dependent [Wirt77]. The difficulty of specification, implementation, and verification of systems increases as parallelism and processing-time dependencies, which are characteristics of embedded systems, are incorporated. In this chapter, we identify the various aspects of embedded and real-time systems that have been addressed in the past few years. In particular, we single out the major research efforts in the development of formal models, specification techniques, verification methodologies, development tools, and operating systems.

### 2.1 Formal Models and Verification Techniques

Time has always been an observable but uncontrollable phenomenon, and unless it becomes possible to travel through it, we will always have to abide by its laws in dealing with "real" problems. Previous studies in modeling real-time systems have focussed on adding the notion of time to formal modeling techniques of traditional systems, namely: logicbased, process-algebra-based, Petri-net-based, and state-based. This view of adding the *time dimension* to all what traditional computing systems research has deemed "good" is yet to be justified.

Verification entails establishing that a solution is correct by showing that it satisfies a set of desired properties. *Formal verification* techniques prove the correctness of a solution by using the rules of a proof system developed for an underlying formal model. *Empirical verification* techniques establish the correctness of a solution using simulation, prototyping, and testing. Despite their elegance, formal verification techniques are not practical for real-world embedded applications. In particular, their soundness depends on how accurate and realistic the adopted abstractions are. In most of the cases, their usefulness is limited to proving properties of specifications rather than implementations.

Properties of embedded systems are usually classified as being either *safety* properties or *timeliness* properties. Safety properties deal with the requirement that "nothing bad will happen", whereas timeliness properties deal with the requirement that "something will happen in due time". It is the timeliness of embedded systems that qualifies them for being real-time systems. Timeliness corresponds to *liveness* – the requirement that "something will eventually happen" – in non real-time systems. Besides liveness, timeliness properties subsume other properties, like fairness and finite progress, often considered in traditional systems. Formal verification of timeliness properties requires proving that specific timing constraints are met. This involves determining the time of completion of actions, which may depend on the pattern and timing of the external environment stimuli, and the availability and capacity of the computing resources.

#### 2.1.1 State-based Techniques

Early attempts at expressing the requirements of real-time systems shared a common view of these systems as Finite State Machines in which a response at any instance is completely determined by the system's present state and its future stimuli [Alfo77, Zave82]. Dasarathy [Dasa85] added *timer alarms* to Finite State Machines to allow for the modeling of real-time telephony systems. A timer alarm is an artificial stimulus that is generated if a specified timing deadline is missed; it acts as an interrupt signaling the occurence of an exception. Lewis [Lewi89] extended finite state graphs with uncertain timing constraints that are expressed as lower and upper delay bounds. This model is used to interpret formulae of branching-time logic, and is the basis for the verification algorithms of timing properties presented in [Lewi90]. Alur, Courcoubetis, and Dill [Alur90] proposed the use of *Timed Büchi Automata* to model the behavior of finite-state asynchronous real-time systems. Timed Büchi Automata are Büchi automata [Bü60] augmented with a mechanism to express constant bounds on the timing delays between system events. They suggested associating each automaton with a finite set of *clocks*, which can be tested or set instantaneously with automaton transitions.

In standard state-based specification techniques, a system is allowed to refuse unspecified inputs. Such specifications, therefore, impose restrictions on what the environment can and/or cannot do. While appropriate for protocol/interface specification, such a methodology seems unrealistic for an embedded systems, where no assumptions can be made about the behavior of the external environment. To avoid this undesirable property, Lynch [Lync88b] proposed the Input-Output Automata (IOA) model in which *inputs* actions are distinguished from *local* actions in that they are always enabled; a transition is defined for any input action and for every state of the automaton. The IOA model was used to develop proof techniques for the study of discrete event systems [Lync88a, Lync89a]. In [Best88a, Best90b] we proposed the Input-Output Timed Automata (IOTA) as an extension to Lynch's IOA model.<sup>1</sup> The IOTA model allows the specification of lower and upper bounds on the delay between the enabling of a locally-controlled action and its firing. Specification and simulation languages, proof techniques, and lower/upper bounds for a number of problems using this and other timed extensions of the IOA model were reported in [Best90a, Lync89c, Lync89b].

State proliferation is a property often attributed to state-based specification and verification techniques. As a remedy, Harel [Hare87] proposed a purely graphic formalism, called *Statecharts*, to reduce the number of states by introducing the multiple active-state notion. Later, Jahanian and Mok [Jaha88] introduced *Modecharts* as a compact and structured way of representing real-time systems. Although similar in some ways to Harel's Statecharts, Modecharts are specifically tailored to representing time-critical systems. The semantics of Modecharts is given in the Real-Time Logic of [Jaha86].

### 2.1.2 Process-Algebra-based Techniques

Several attempts have been made to extend traditional process-algebra techniques [Henn88] to represent time. The work of Reed and Roscoe [Reed88], extending Hoare's Communicating Sequential Processes (CSP) model [Hoar85], and the work of Baeten and Bergstra [Baet91c], extending Bergstra and Klop's Algebra of Communicating Processes (ACP) [Berg84] are two such examples.

In [Gerb89b], Gerber, Lee, and Zwarico suggest using the *Timed Acceptances Model* to capture the temporal constraints of concurrent programs. Their model, which they use to prove correctness properties of real-time programs, consists of a CSP-based language, a partially ordered semantic model, and an axiom system. Similar efforts have been reported in [Gosw88] using a simpler semantic domain. In an effort to bridge the gap between computational models and implementation environments, Lee, Gerber, and Davidson proposed

<sup>&</sup>lt;sup>1</sup>Similar extensions to Lynch's IOA model were reported independently by Tuttle, Modugno, and Merritt in [Tutt88].

the *Communicating Shared Resources* (CSR) model [Gerb89a, Gerb90]. The CSR model is synchronous. It allows processes to be assigned to resources and execute thereon in an interleaved fashion according to their priorities. In order to allow for formal verification capabilities, they developed a Calculus for CSR (CCSR). CSR specifications can be translated into the CCSR formalism for verification using syntactic manipulations [Lee91].

A particularly interesting work is that of Baeten and Bergstra [Baet91b], in which their real time process algebra  $(ACP_{\rho})$  [Baet91c] is extended into a real space-time process algebra  $(ACP_{\delta\rho})$ , where processes are described using both space and time coordinates. This work is a first step toward tackling some of the concerns addressed in this thesis, namely *physical correctness*. Two versions of  $ACP_{\delta\rho}$  are developed, namely *classical* and *relativistic*. In [Baet91a], the classical version is used to study asynchronous communication in such a way that the motion of processes can be taken into account.

#### 2.1.3 Logic-based Techniques

Temporal logics are appropriate for the description of the temporal properties of systems. In [Pnue77], Pnueli advocated the use of temporal logic formalisms for the behavioral specification of concurrent systems. He described a time hierarchy of specifications relating the occurence of time in formulae of a system to the expressive power of that system. Many interesting properties – like safety, liveness, and precedence – can be proved using such formalisms [Bern81, Mann82]. For example, Bochmann [Boch82] used temporal logic to specify and verify properties of an arbiter. Along the same lines, Clarke et al. [Mish83, Clar83] proposed the use of temporal logic in the automatic verification of asynchronous circuits. Moszkowski [Mosz85] defined a temporal logic to reason about hardware at the circuit level. Jahanian and Mok [Jaha86] proposed a first-order Real-Time Logic (RTL) to aid in the safety analysis of timing properties of real-time systems. Their model does not have modal operators to deal with time; instead, time is captured by a function that time-stamps events. Time constraints are expressed as first order assertions on these functions. Later, they used their logic in conjunction with Modechart specifications [Jaha88]. Allen [Alle81, Alle83, Alle84] proposed an interval temporal logic that is based upon time intervals rather than time points; it axiomatizes and uses seven relationships,

with inverses, that can hold between two time intervals. This approach enables reasoning about non-instantaneous actions, for example in hardware specification [Wils89, Wils90] and in plan generation [Alle86].

A critical deficiency of temporal logics is their inability to express causal relationships between the various events in a system. Recently, Borriello and Amon [Borr90] addressed that problem by proposing a model for the executable specification of timing behavior that is based on a restricted version of the full first-order predicate calculus and which utilizes event ancestry<sup>2</sup> for the representation of complex timing relationships.

### 2.1.4 Petri-net-based Techniques

Petri-nets are attractive candidates for the specification of real-time systems. In particular, they offer an expressive technique for the representation of data dependencies and causality. There have been several proposals for extending the standard Petri-net model to include time. Ramchandani [Ramc74] proposed associating computational delays with transitions. Merlin and Farber [Merl74, Merl76] suggested the use of minimum and maximum bounds on uncertain transitional delays. Associating delays with Petri-net's transitions violates the instantaneous firing feature of the basic Petri-net model. This was remedied in the work of Sifakis [Sifa77] and, later, in the work of Coolahan and Roussopoulos [Cool83], by associating computational delays with places rather than transitions. Razouk [Razo83] proposed the use of both enabling and firing times; tokens are absorbed from input places after the enabling time has elapsed and do not reappear in the output places until after the firing time has elapsed. Ghezzi et al. [Ghez89] proposed a model where tokens are time-stamped environments; time constraints are associated with transitions and are modeled as predicates on the input tokens.

Timed Petri-net models have been used in studying various aspects of real-time systems – requirement specification [Cool83], performance evaluation [Holl87], and safety analysis [Leve87], to name a few.

<sup>&</sup>lt;sup>2</sup>a weak notion of causality

### 2.2 Specification Techniques

The usual approach for specifying computing systems behavior is to enumerate the actions that a system participates in [Henn88, Lync89a]. Time is only perceived through the partial or total ordering of these actions. Such an ordering may be determined, not by the time in which actions were taken, but according to other considerations such as consistency [Eswa76] and serializability [Papa79, Yann84]. This artificial reordering of actions is only possible in applications where assumptions about the outside world can be made and enforced.<sup>3</sup> For embedded systems, such assumptions cannot be accommodated; time, as viewed by the environment in which a program executes, is a significant factor. Thus, the main challenge in the specification of real-time systems is how to incorporate the notion of time – how to extend programming notations to allow programmers to specify computations that are both *dependent* and *constrained* by time.

Complexity is another consideration in the specification of embedded systems. To manage a large and complex system, it is a good practice to hierarchically decompose it so that details be hidden from the higher levels of abstraction and exposed at the lower ones. This methodology allows implementors to reason about and establish the correctness of subsystems at each level independently. To deduce properties of the whole system from properties of its parts and the way these parts are combined, we must characterize a way to *compose* the real-time properties of parts to synthesize them for the whole. This might be subtle because these parts interact in ways that depend on resource and time constraints.

#### 2.2.1 Requirement Specification Languages

Requirement specifications act as a contract between the customer and implementor of a system. There are two approaches for requirement specifications. In the conventional approach, systems are treated as black boxes; only the required characteristics of their external behavior are described – usually partially and informally. In the operational approach [Zave82], requirements are specified by formulating a system – using implementation-independent

<sup>&</sup>lt;sup>3</sup>For instance, by undoing actions and aborting transactions in a database system

structures – that would generate the desired behaviors. In adopting one of these two approaches, one has to take into account several considerations, namely validation, verification, automation, maintenance, and management [Zave84]. We argue that, for embedded systems, the operational approach is appropriate. Its executable nature facilitates the validation process; its formality promises greater verification potentials; its modularity makes the evolution of customers' requirements easier to manage and encourages automation by advocating reusability and step-wise refinement.

The PAISLey language and environment [Zave84, Zave86, Zave88] were crafted with the operational requirements specification approach in mind. A system is described by a set of asynchronous processes, where each process has a state and goes through a sequence of discrete state changes (process steps). The computations occurring during these steps are specified using a functional notation to represent mappings. An upper bound, lower bound, or distribution of possible computational delays can be attached to any mapping. Only non-recursive time-constrained mappings are allowed. Special mappings called exchange functions are used to support interprocess interactions.<sup>4</sup> An exchange function is evaluated - even if its value is not needed - to produce global side-effects of synchronization and communication. The PAISLey environment provides tools for the execution of potentially incomplete specifications and testing for inconsistencies. Although designed for embedded applications, PAISLey fails in many respects. Time is added as an afterthought, time-constraints cannot be state-dependent, the notion of causality is non-existent, communication is blocking, broadcasting is not allowed, the use of exchange functions defeats the referential transparency property, and the functional flavor of PAISLey is not appropriate for the object-oriented/procedural nature of embedded systems.

ENCOMPASS is an environment aimed to support the incremental construction of Ada programs using executable specifications and formal techniques [Terw87a, Terw88]. It provides support for various aspects of software development including, specification, prototyping, testing, formal verification, documentation, configuration control and project management. In ENCOMPASS, software can be specified using PLEASE [Terw87c, Terw87b] an Ada-based executable specification language which can be automatically translated into

<sup>&</sup>lt;sup>4</sup>Exchange functions are very similar to the CSP input and output primitives [Hoar85].

Prolog. In ENCOMPASS, software components are first specified using a combination of conventional programming languages and predicate logic. These abstract components are then incrementally refined into components in an implementation language. Each refinement is verified before another one is applied which guarantees that the final components satisfy the original specification. PLEASE allows a procedure or function to be specified with pre- and post-conditions written using Horn clauses. PLEASE specifications may be used in proofs of correctness. They may also be transformed into prototypes which use Prolog to execute pre- and post-conditions. ENCOMPASS and PLEASE were designed with the "software engineering" problem in mind. They do not support any notion of time, distribution or parallelism.

RT-ASLAN is a state-based formal language for specifying real-time systems at different levels of abstractions with the motivation of verifying them [Auer86]. A real-time system is viewed as a set of processes communicating via an *interface process*. Process' transitions can be either periodic or non-periodic. Time is maintained by a process that increments a time variable after each *tick* transition. Assertions written in first-order predicate logic can be attached to RT-ASLAN specifications. Assertions denote either *invariants* or *constraints*. Verification is done using a state-based inductive approach with the tick transition as the inductive step. In addition to its non-realistic communication and time management assumptions, a number of other simplifying assumptions are made in RT-ASLAN.<sup>5</sup>

### 2.2.2 Programming Languages

Until recently, most of the time-critical parts of an embedded application were (and are still being) implemented in low-level assembly or machine languages. This is primarily caused by a common misconception that "real-time computing is equivalent to fast computing" [Stan88a]. The objective of real-time computing is to meet the specified timing requirements. A faster computer makes it easier to meet these requirements, but does not guarantee it. The most important property of real-time programming languages is, thus, predictability.

<sup>&</sup>lt;sup>5</sup>For example, each process is assumed to run on a dedicated processor, thus systems that can be specified using RT-ASLAN are neither process nor resource restricted.

With few exceptions, most of the real-time programming languages developed for embedded applications failed to meet that single property. For example, Ada is designed for embedded time-critical applications and is intended to support static priority scheduling of tasks. However, the definition of Ada tasking allows a high-priority task to wait for a low-priority task for an unpredictable duration. Ada and Modula-2 are examples of early attempts at developing general-purpose real-time programming languages. Logically correct programs are written using mechanisms such as coroutines, processes, priorities, interrupts, and exception handling to control the execution behavior. Knowledge of the runtime environment is required to tailor the program to meet timing specifications, which makes the program sensitive to hardware characteristics and system configuration.

Other factors – besides efficient coding and hardware characteristics – determine predictability. Implementation languages should be expressive enough to prescribe complex timing constraints. Current real-time programming languages provide little (if any) support for expressing time constraints. This state of affairs is very well pronounced in Berry et al.'s heavily quoted statement [Berr83]: "...paradoxically, one can verify that the current so-called 'real-time programming languages' do not provide any explicit means of correctly expressing time constraints. A fortiori, they provide no insurance that the constraints would be respected when executing the program." For example, in a language like Ada where only lower bounds on time delays can be expressed, there is no way upper bounds can be asserted.

Esterel [Berr85] represents the first attempt at permitting direct expression of timing requirements in programs. Programmers are allowed to specify deadlines for procedural invocations, leaving for the runtime system the responsibility to ensure their satisfaction. In addition to the timing requirements, programmers are allowed to specify exception handlers to be invoked if the specified requirements cannot be honored at run-time. The lack of compile-time analysis in Esterel, however, means that predictability, in the strong sense of completing without exception, is lost.

One way to insure predictability is to restrict expressiveness. This is the approach taken by Real-Time Euclid [Klig86]. The language definition forces every use of its constructs to be both time- and space-bounded, thus avoiding many of the dynamic aspects found in languages designed for programming traditional systems – recursion for example.

Time bounds and time-out exception handlers have to be specified for unbounded loops, wait statements, and device requests. Real-Time Euclid programs can, thus, be analyzed for guaranteeing schedulability given a specific hardware organization.

Another approach to guarantee that stringent timing constraints are always met is to sacrifice accuracy for predictability. This approach forms the basis for the body of research on *imprecise computations* [Lin87, Liu91]. The imprecise computation techniques prevents timing faults and achieves graceful degradation by producing approximate results of acceptable quality whenever exact results cannot be produced in time. The Flex language [Lin88, Lin91] is intended for systems where the this methodology is applicable. Three main techniques are used to specify time-constrained computations in Flex. The *milestone method* is appropriate for monotone time-critical tasks. A task is monotone if the quality of its intermediate result does not decrease as it executes longer. Flex provides constructs for the specification of intermediate result variables and error indicators. Should the task terminate prematurely due to a hard time constraint, the latest recorded intermediate results and error indicators are readily available. Another technique for trading off quality for time is the *sieve method* in which, if needs be, computation steps can be skipped to save time. In applications where the milestone and sieve methods are not applicable, the multiple version method is used. Using this approach, programmers specify two (or more) versions for each time-critical task. At run-time, the appropriate version is chosen based on the available time to produce a result. The imprecise computations approach warrants more scheduling flexibility in order to meet deadlines. In [Liu87, Chun90, Shih91] various algorithms for scheduling imprecise computations are presented.

The real-time programming languages we discussed thus far are all imperative. In [Faus86], Faustini and Lewis show how to extend Lucid, an equational dataflow language, for real-time purposes. In Lucid, programmers think in terms of streams and filters. A filter is used to construct one *output stream* out of a number of *input streams*, each with known properties. A Lucid program is, thus, a set of equations modeling a dataflow graph. Time is incorporated in a Lucid program by associating a stream of *time windows* with each stream of data values. Attaching time windows to input and output streams can be viewed as imposing timing constraints on their generation. Another similar language

is LUSTRE [Caps87], a synchronous data-flow language aimed for programming real-time systems. LUSTRE is primarily designed for mathematically describable systems.<sup>6</sup> A program is a system of time-dependent equations representing *invariant assertions* that hold at each point in time. In LUSTRE there is no notion of execution, control or sequentiality. Only discrete systems are considered. Thus, time is projected onto the set of naturals and variables are infinite sequences of values. The equational semantics of Lucid and LUSTRE is much too simple to be practically usable in complex systems. In particular, some tasks cannot be fully described using systems of equations. A solution suggested in [Caps87] is to allow a LUSTRE program to call external functions written in a host language (namely C). To preserve the equational semantics, these external functions have to compute in zero time and have to produce no side-effects. Both of these assumptions are unacceptable for embedded real-time applications.

Computations in embedded systems are likely to be not only *time-constrained* but also *time-dependent*. ARCTIC [Rubi87] is an example for a language for describing the behavior of time-dependent concurrent activities. The fundamental idea in ARCTIC is that variables, and behaviors in general, can be described using functions of time. In ARCTIC, timing is explicitly indicated and is not a consequence of sequential execution. ARCTIC provides a set of tools to describe continuous as well as discrete signals. It has been used in the production of computer music and other digital audio sounds.

### 2.3 Development Support

The increasing complexity of embedded real-time systems dictates that powerful tools be available to aid in their design, implementation, and support. In particular, programming environments must provide powerful tools for testing, debugging, and simulating the operation of real-time programs. Also, they must facilitate the reuse, adaptation and tailoring of real-time software modules. In the past, these activities were done mostly in an ad hoc manner.

<sup>&</sup>lt;sup>6</sup>For example, automatic control and signal processing applications.

### 2.3.1 Operating System Kernels

Operating systems play a key role in managing system resources so that programmers can focus on the application specific problems rather than the underlying system issues. Typically, real-time operating systems will have to allocate resources, keep track of deadlines and raise exceptions in case they are not met. In embedded and real-time systems, however, the operating system and the application are tightly intertwined and it is not clear how they can be decoupled. This represents a dilemma and, thus, a challenge; how to provide high level abstractions for programmers and yet meet performance requirements which are fundamentally dependent on the implementation and the environment. Abstractions, like processes, fairness, and finite progress, although useful in connection with conventional operating systems, are not necessarily adequate for time-critical applications [Schn88]. Current operating systems offer no solutions for the aforementioned dilemma; they are inadequate and must evolve to cope with the demands of real-time programmers.

Most of the existing real-time kernels are simply stripped down, optimized versions of conventional timesharing operating systems. VRTX [Read86], VxWorks [Wind89], and Lynx [Baue90] are classic examples. They promote a hardware independent architecture that is independent from the file system and the I/O system. Their prominent features include fast context switching, efficient interrupt handling, fast data-acquisition, real-time clock support, user-defined watchdog timers and interrupts, and priority scheduling. In an effort to provide a basis for evaluating such operating systems, POSIX.4 and an extension thereof have been proposed as IEEE standards [IEEE90]. Compliance with the POSIX standards is expected to rapidly become mandatory for commercial systems [Gall91].

REX [Bake86] promotes a different kernel structure. It introduces the notion of an *executive* – a software layer that runs on top of an operating system and which is responsible for scheduling and storage management. An executive acts as an interface between applications and the lower level operating system functions such as interrupt handling. CHAOS [Schw87] and AT&T's NRTX [Cox88] are similar kernels in that they offer an object-based view of embedded systems. Such a view promises significant improvement in modularity, reconfigurability, and maintainability. Both systems are aimed at robotics applications.

CHAOS evolved from an earlier kernel called GEM. It provides programmers with a view of the system as a set of interacting objects. NRTX is a real-time executive derived from UNIX<sup>TM</sup>. Along with  $C^{++}$ , it offers a programming environment for the development of software for embedded systems. The Spring kernel [Stan87, Stan89] is built around the relatively new principle of *segmentation*, in which resources are divided into units to be manipulated by the various parts of the kernel – the scheduler, for example – in such a manner as to provide predictability with respect to timing constraints [Stan88b].

An additional responsibility for real-time operating systems is the management of information about the real-world and/or any active real-time tasks. This information should be viewed as a shared resource that multiple processes (including the operating system itself) might want to access (read or update) concurrently. This access, however, has to be regulated to insure some level of consistency and recency. In real-time systems, a significant portion of the data acquired from external interfaces is highly perishable in the sense that it has value to the mission only if used quickly. To satisfy timing requirements, the degree of concurrency must be increased through some kind of interaction between concurrency control protocols and real-time scheduling algorithms. It is not clear whether the classical theory of concurrency control (the serializability theory) [Papa79, Yann84] is appropriate for embedded systems. We believe it is not because of the limitation in concurrency allowed by serializable concurrent executions.

### 2.3.2 Scheduling Algorithms

The scheduling problem is that of allocating the available limited resources in a way that guarantees the satisfaction of the specified timing constraints. This can be done either by the programmer or by the run-time system. These two choices represent the extremes of a continuum. Scheduling for real-time systems is very different from scheduling problems considered in other areas where the goal is to find an optimal *static* scheduling policy that would minimize the response time for a given set of tasks. In real-time systems, the major goal is to schedule as many jobs as possible, subject to meeting deadlines. This does not necessarily mean minimizing response times. In addition, real-time systems are highly dynamic, thus requiring adaptive scheduling algorithms.

The interaction between verification and scheduling in real-time systems is subtle. This is basically due to the fact that scheduling affects the timing properties of programs and it is these properties that should be verified. On the one hand, one might think of the verification process as one in which, given the problem specification and the available resources, it is required to show the *existence* of at least one schedule that satisfies the specifications. In this case, the job of the scheduler is to find such a schedule. On the other hand, we might assume that the scheduling policy is known and thus verifying the correctness of a program entails showing that the *composition* of the program, scheduling policy and available resources meets the given specifications. This latter approach is both appealing and realistic. It is appealing because it allows the exposure of the available resources to the verification process, thus making it possible to provide clues about the minimum required resources and to compare different design alternatives. It is realistic because in almost all real-time application, the scheduling policy is usually predetermined.<sup>7</sup> The challenge in adopting this approach, though, is the need to represent programs, schedulers and available resources in a unified framework.

### 2.4 Other Issues

Embedded and real-time computing is a wide open research area for intellectually challenging computer science problems. There are a number of aspects and research areas of real-time systems that we have not considered in our review as they are not directly related to our work. These include programming environments, databases, artificial intelligence, general and special purpose architectures, communication protocols, fault-tolerance, testing, and safety analysis. An overview of these research areas and others can be found in [Stan88b, Stan92, Burn90, Tilb91a, Tilb91b].

<sup>&</sup>lt;sup>7</sup>Usually based on some priority scheme.

## Chapter 3

# The Time-constrained Reactive Automata Model

Using the TRA model, an embedded system is viewed as a set of asynchronously interacting automata (TRAs), each representing an autonomous system entity. TRAs are input enabled; they interact asynchronously by signaling events on their output channels and by responding to events signaled on their input channels. The behavior of a TRA is governed by time-constrained causal relationships between computation-triggering events. The TRA model is compositional and allows time, control, and computation nondeterminism. Among its salient features, the TRA model allows the specification of only those systems that are potentially physically realizable. In that respect, it abides by the causality and spontaneity principles. The TRA model [Best91b] has evolved from our work in [Best90b] extending Lynch's IOA model [Lync88b, Lync88a] to suit embedded and time-constrained computation.

### 3.1 Novelties

Previous studies in modeling real-time computing have focussed on adding the notion of time without regard to physical properties of the modeled systems. This makes it possible to specify systems that do not abide by principles like causality and spontaneity. Our work remedies such situations by dealing not only with the notion of time, but also with the notion of space. Events occur at uniquely identifiable points in time as well as in space. Events occurring at the same time and place are undistinguishable. The payoff for the dual treatment of space and time is manifold. For example, requirement specifications become more expressive since they can constrain the time as well as the space coordinates of system events. Also, mappings between various levels of abstractions for compilation and verification purposes become more robust as the formalism becomes more structured.

The TRA model differs from others in that it does not allow the specification of systems that are not *reactive*. A system is reactive if it cannot block the occurence of events not under its control. This property is crucial for accurate and realistic modeling of embedded and real-time systems. A sufficient condition for reactivity is the *input enabling* property proposed in [Lync88b]. The TRA model is input enabled. It distinguishes clearly between environment-controlled actions, which cannot be restricted or constrained, and locally-controlled actions, which can be scheduled and disabled.

Among state-based models, the TRA formalism is unique in that it admits the causal nature of physical processes. The *causality* of the TRA model follows the standard definition of causality for non-deterministic systems. A system is *causal* if given two inputs that are identical up to any given point in time, there exist outputs (for the respective inputs) that are also identical up to the same point in time. The TRA model enforces causality by requiring that any locally-controlled actions be produced only as a *result* of an earlier *cause*. In our work, a clear distinction is made between causality and dependency. An event occurs as a result of exactly one earlier event but may depend on many others as reflected in the state of the system. This spares our formalism from dealing with clairvoyant and capricious behaviors [Stua91].

Spontaneity is a notion closely related to causality.<sup>1</sup> A system is spontaneous if its output actions at any given point in time t cannot depend on actions occuring at or after time t. In particular, if an output occurs simultaneously with (say) an input transition, the same output could have been produced without the simultaneous input transition [Sree90]. Simultaneity is, thus, a mere coincidence; the output event could have occured spontaneously even if the input transition was delayed. The TRA model enforces spontaneity by requiring that simultaneously occuring events be independent; time has to necessarily advance to observe dependencies.

The TRA model distinguishes between two notions of time: *real* and *perceived*. Real time cannot be measured by any single process in a given system; it is only observable by the environment. Perceived time, on the other hand, can be specified using uncertain time delays. The TRA model, therefore, does not provide for (or allow the specification of) any *global* or *perfect clocks*. As a consequence, the only measure of time available for system processes has to be relative to *imperfect, local clocks*. This distinction between real time and perceived time is important when dealing with embedded applications where time properties are stated with respect to real time, but have to be preserved relying on perceived time.

### 3.2 The TRA Model

An embedded system is viewed as a set of asynchronously interacting Mealy [Hopc79] automata (TRAs), each representing an autonomous system entity. TRAs are input enabled; they communicate by signaling events on their output channels and by reacting to events signaled on their input channels. The behavior of a TRA is governed by time-constrained causal relationships between computation-triggering events. The TRA model is compositional and allows time, control, and computation non-determinism. In this section, we formally define the TRA model.

<sup>&</sup>lt;sup>1</sup>Actually both spontaneity and causality are directly related to the past and future light cones of an event in space-time [Hawk88].

#### 3.2.1 Basic Definitions

We adopt a continuous model of time similar to that used in [Alur90, Lewi90], where time is considered a measurable, continuous, infinitely divisible quantity. We represent any point in time by a nonnegative real  $t \in \Re$ . Time intervals are defined by specifying their end-points which are drawn from the set of nonnegative rationals  $\mathcal{Q} \subset \Re$ . A time interval is viewed as a traditional set over nonnegative real numbers. It can be an empty set, in which case it is denoted by  $\varepsilon$ , it can be a singleton set, in which case it is denoted by the  $[t, t], t \in \mathcal{Q}$ , or else it can be an infinite (dense) set, in which case it is expressed in one of the following formats  $[t_l, t_u], (t_l, t_u], [t_l, t_u), \text{ or } (t_l, t_u)$ , denoting the closed, right-closed, left-closed, and open time intervals, respectively, where  $t_l, t_u \in \mathcal{Q}$  and  $t_l < t_u$ . We use  $|[t_l, t_u]|$  to denote a dense time interval in any one of these formats. The set of all dense time intervals is denoted by  $\mathcal{D}$ . Throughout this thesis, we use the symbol  $\delta$  to denote a time interval and the symbol  $\Delta$  to denote a set of such time intervals.

Let  $\delta_i = |[t_a, t_b]|$  and  $\delta_j = |[t_c, t_d]|$  be two dense intervals. We say that  $\delta_i$  contains  $\delta_j$  if  $\delta_j \subseteq \delta_i$ . The union, intersection, and difference of  $\delta_i$  and  $\delta_j$  are denoted by  $\delta_i \cup \delta_j$ ,  $\delta_i \cap \delta_j$ , and  $\delta_i - \delta_j$ , respectively.<sup>2</sup> We define the sum of  $\delta_i$  and  $\delta_j$  to be the new time interval  $\delta_k = \delta_i + \delta_j$  whose end-points are obtained by adding the corresponding end-points of  $\delta_i$  and  $\delta_j$ , namely  $\delta_k = |[t_a + t_c, t_b + t_d]|$ . As a special case, we define the time interval  $\delta_k$  obtained by shifting the time interval  $\delta_i$  by  $\tau$  to be  $\delta_k = \delta_i + \tau = \delta_i + [\tau, \tau] = |[t_a + \tau, t_b + \tau]|^2$ .

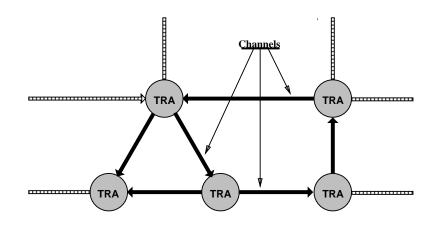

A real-time system is viewed as a set of interacting automata called TRAs (Timeconstrained Reactive Automata). TRAs communicate with each other through *channels* (see Figure 3.1). A channel is an abstraction for an *ideal* unidirectional communication. The information that a channel carries is called a *signal*, which consists of a sequence of *events*. An event, denoted by  $\langle \pi : t \rangle$ , underscores the occurence of an *action*  $\pi$  at a specific point in time t.

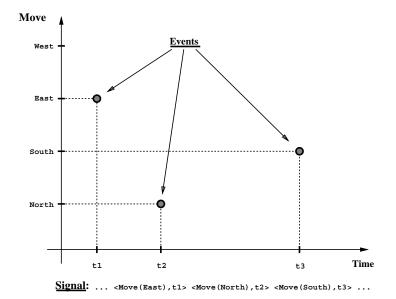

To illustrate the notions of actions, events, and signals (see Figure 3.2), consider the channel MOVE of some TRA. Let North, South, East, and West be the possible values that can be signaled on MOVE. MOVE(East) is, therefore, a possible action of the TRA. The

<sup>&</sup>lt;sup>2</sup>The format of the resulting set (closed, semi-closed, or open) depends on the formats of  $\delta_i$  and  $\delta_j$ .

instantiation of MOVE(East) at time  $t_1$  denotes the occurrence of an event  $\langle \text{MOVE(East)} : t_1 \rangle$ . Furthermore, the sequence of events  $\langle \text{MOVE(East)} : t_1 \rangle \langle \text{MOVE(North)} : t_2 \rangle \langle \text{MOVE(South)} : t_3 \rangle$  $\dots etc.$  constitutes a signal. Events occurring on different channels can be simultaneous. We use  $\langle \pi_1, \pi_2, \dots, \pi_m : t \rangle$  to denote the occurrence of the set of simultaneous events  $\langle \pi_1 : t \rangle$ ,  $\langle \pi_2 : t \rangle, \dots, \langle \pi_m : t \rangle$ .

Figure 3.1: TRA objects and channels.

Figure 3.2: Signals, events, and actions.

To be identifiable, events on a given channel must be signaled at different points in time. Simultaneity can only be observed between events fired on different channels. Therefore, a signal  $\langle a_0 : t_0 \rangle \langle a_1 : t_1 \rangle \dots \langle a_k : t_k \rangle \dots$ , is totally ordered  $(t_k < t_{k+1}, k \ge 0)$ . In an earlier model [Best90b], we enforced this requirement by associating a minimum *switching time* with every channel; two events signaled on the same channel have to be separated by an amount of time equal to at least the minimum switching time. Imposing a finite positive switching time means that channels have *finite* capacities and thus cannot carry infinitely many events at the same time. Associating a lower bound on the switching time of input channels, however, seemed to violate the input-enabled principle. This is why, in the TRA model, we only require that a *positive* (rather than minimum) switching time exist.

At any point in time, a TRA is in a given *state*. The set of all such possible states defines the TRA's *state space*. The state of a TRA is visible and can only be changed by local *computations*. Computations (and thus state transitions) are triggered by actions and might be required to meet specific *timing constraints*.

In the following presentation we use capital letters (e.g.  $\Theta, \Gamma, \Delta$ ) to denote sets, and small letters (e.g.  $\theta, \gamma, \delta$ ) to denote members of these sets. For example, we use  $\Theta$  to denote a set of states, and  $\theta$  to denote an element of  $\Theta$ . Subscripted capital letters are used to denote subsets. For example,  $\Theta_i$  denotes a subset of the set  $\Theta$ . We use superscripts to identify sets belonging to a given TRA object. For example,  $\Theta^{\mathcal{A}}$  denotes the set of states associated with the TRA  $\mathcal{A}$ . Superscripts are dropped whenever the association is understood from the context. The dimensionality of a cross-product  $\Theta = \Xi_1 \times \Xi_2 \times \ldots \times \Xi_n$  is *n*. Furthermore, if  $\theta \in \Theta = (\xi_1, \xi_2, \dots, \xi_n), \xi_i \in \Xi_i$ , where  $1 \leq i \leq n$ , then the r<sup>th</sup> component of  $\theta$  (namely  $\xi_r$ ) is denoted by  $\theta[r]$ . A sequence s is an ordered string of symbols taken from an alphabet A. The set of all the prefixes of a sequence s is denoted by pref(s) and the set of all the prefixes of any sequence in a set S is denoted by pref(S). The catenation of two sequences  $s_1$  and  $s_2$  is denoted by  $s_1s_2$ . An empty sequence is denoted by  $\perp$ . The cardinality of a set  $\Theta$  is denoted by  $|\Theta|$ ; its power set is denoted by  $2^{\Theta}$ . The sets of natural, integer, rational, and real numbers are denoted by  $\mathcal{N}, \mathcal{Z}, \mathcal{Q}$ , and  $\Re$ , respectively. The set  $\phi$  denotes an empty set. We generalize a function  $f: A \to B$  over subsets of its domain A by defining  $f(A') = \bigcup_i f(a_i)$ , where  $a_i \in A' \subseteq A$ .

#### 3.2.2 The TRA Object

In this section we formally define the various components of a TRA object and informally introduce its operational behavior. A formal treatment of the operational semantic of a TRA object will be given in section 3.4.

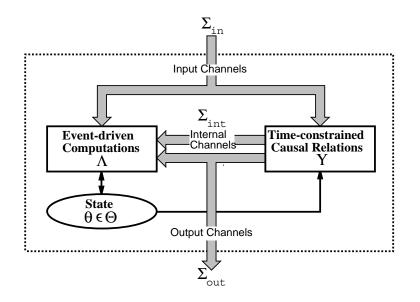

**Definition 1** A TRA  $object^3$  is a sextuple  $(\Sigma, \sigma_0, \Pi, \Theta, \Lambda, \Upsilon)$ , where

- Σ, the TRA signature, is the set of all the channels of the TRA. It is partitioned into three disjoint sets of input, output, and internal channels. We denote these by Σ<sub>in</sub>, Σ<sub>out</sub>, and Σ<sub>int</sub>, respectively. The set consisting of both input and output channels is the set of external channels (Σ<sub>ext</sub>). These are the only channels visible from outside the TRA. The set consisting of both output and internal channels is the set of local channels (Σ<sub>loc</sub>). These are the locally controlled channels of the TRA.

- $\sigma_0 \in \Sigma_{in}$  is the start channel.

Figure 3.3: Basic components of a TRA object.

<sup>&</sup>lt;sup>3</sup>see Figure 3.3 for an illustration.

- Π, the signaling range function, maps each channel in Σ to a possibly infinite set of values that can be signaled as actions on that channel. Action sets of different channels are disjoint. The set of all the actions of a TRA is given by Π(Σ). The set of input, output, internal, external, and local actions are similarly given by Π(Σ<sub>in</sub>), Π(Σ<sub>out</sub>), Π(Σ<sub>int</sub>), Π(Σ<sub>int</sub>), and Π(Σ<sub>ioc</sub>), respectively.

- Θ is a possibly infinite set of states of the TRA. The set Θ can be expressed as the cross product of a finite number of subspaces Θ = Φ<sub>1</sub> × Φ<sub>2</sub> × ... × Φ<sub>p</sub>, where p ≥ 1 denotes the dimensionality of Θ.

- Λ ⊆ Θ × Π(Σ) × Θ is a set of possible computational steps of the TRA. TRAs are input enabled which means that for every π ∈ Π(Σ<sub>in</sub>), and for every θ ∈ Θ, there exists at least one step (θ, π, θ') ∈ Λ, for some θ' ∈ Θ. Thus, Λ defines a total multifunction Λ : θ × Π(Σ<sub>i</sub>n) → θ.